از متغیرها برای ذخیره سازی محلی در دستورات و پروسس و زیر برنامه ها استفاده می شود. برخلاف سیگنال ها که مقادیرشان را برای آینده زمان بندی می کنند، هر انتساب به متغییر بی درنگ رخ می دهد.

اعلان یک متغییر به صورت زیر است:

VARIABLE variable_name {,variable_name} : variable_type[:=value];

پس از کلید واژه VARIABLE یک یا چند نام متغیر می آید. هر نام، متغیر جدیدی ایجاد می کند. سازه variable_type نوع داده متغیر را تعریف می کند، و یک مقدار اولیه اختیاری را نیز می توان مشخص کرد. متغیرها را فقط می توان در بخش های اعلانی پروسس و زیر برنامه اعلان کرد. مثال زیر از دو متغیر استفاده می کند:

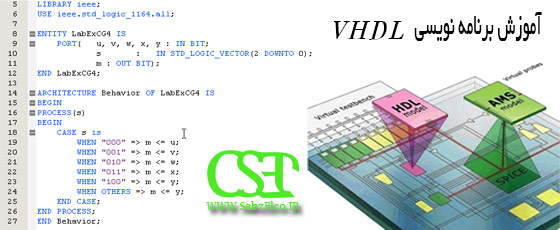

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; ENTITY and5 IS PORT ( a, b, c, d, e : IN std_logic: q : OUT std_logic); END and5; ARCHITECTURE and5 OF and5 IS BEGIN PROCESS(a, b, c, d, e) VARIABLE state : std_logic; VARIABLE delay : time; BEGIN State := a AND b AND c AND d AND e; IF state = ‘1’ THEN Delay := 4.5 ns; ELSEIF atate = ‘0’ THEN Delay := 3 ns; ELSE Delay := 4 ns; END IF; q <= state AFTER delay ; END PROCESS; END and5;

این مثال یک معماری برای گیت AND پنج ورودیست. در بخش اعلانی پروسس دو متغیر state و delay اعلان می شوند.

متغیر state به عنوان حافظه ای موقتی برای نگداری مقدار تابع AND ورودی ها استفاده می شود. مقدار حافظه موقتی delay برای نگهداری مقدار تاخیری استفاده می شود که هنگام زمان بندی مقدار خروجی استفاده خواهد شد.

هیچ یک از این متغیرها نمی توانند داده ایستا باشند زیرا مقادیر آنها به مقدار ورودی های a ، b ، c ، d و e وابسته است. از سیگنال ها نیز می توان برای ذخیره سازی داده استفاده کرد، اما به چند دلیل این کار انجام نمی شود:

-متغیرها به طور ذاتی کارامدترند زیرا انتساب به آنها بی درنگ انجام می شود، در حالی که وقوع سیگنال بایستی زمان بندی شود.

-متغیرها حافظه کمتری اشغال می کنند، در حالی که سیگنال ها به اطلاعات بیشتری برای زمان بندی و خواص سیگنال نیاز دارند.

-برای همگام سازی انتساب سیگنال با دلتای زمانی اجرای آن به یک دستور WAIT نیاز است.

هرگاه یکی از سیگنال های ورودی a ، b ، c ، d و e تغییر کند، پروسس احضار می شود. به متغیر state مقدار AND تمام ورودی ها تخصیص می یابد. سپس، بسته به مقدار متغیر state تاخیری به متغیر delay تخصیص می یابد.

بسته به سیگنال تخصیص یافته به متغیر delay ، مقدار متغیر state به سیگنال خروجی q تخصیص می یابد.

ثابت ها

ثابت ها نام هایی می باشند که به مقادیر مشخصی از یک نوع تخصیص می یابند. طراح می تواند به کمک ثابت ها مدلی با مستندات بهتر داشته باشد که به روز رسانی آنها ساده تر است.

برای مثال، اگر در چند نمونه به مقدار ثابتی نیاز باشد، باید از یک ثابت استفاده کرد. طراح می تواند مقدار ثابت را تغییر داده و با کامپایل مجدد کد، تمام نمونه های مقدار ثابت را برای انعکاس مقدار جدید را به روز رساند.

همچنین، یک ثابت با قابل فهم کردن مقدار توصیه شده، مدلی با مستندات بهتر فراهم می کند. به عنوان مثال، به جای استفاده مستقیم از مقدار 3.1414 در مدل، طراح باید ثابتی به صورت زیر ایجاد کند:

CONSTANT PI : REAL := 3.1414;

هر چند مقدار تغییر نمی کند، اما خوانایی مدل افزایش می یابد.

اعلان یک ثابت به صورت زیر است:

CONSTANT constant_name {,constant_name} : type_name [:=value];

مشخصه Value اختیاریست زیرا VHDL ثابت های معوق را نیز پشتیبانی می کند. ثابت های معوق در اعلان بسته اعلان، و مقدارشان در بدنه بسته مشخص می شود.

ثابت ها از نظر حوزه بندی مشابه سیگنال ها می باشند. اگر بسته توسط چند موجودیت استفاده می شود ثابت اعلان شده در بسته می تواند سراسری باشد.

تمام معماری های موجودیت می توانند از ثابت اعلان شده در بخش اعلان موجودیت استفاده کنند. ثابتی که در یک معماریست می تواند توسط تمام دستورات درون موجودیت، از جمله دستور پروسس، استفاده شود.

ثابتی که در اعلان پروسس اعلان می شود فقط در پروسس قابل استفاده است.

این آموزش بیش از ۳ سال قبل ارسال شده و اکنون در لیست بهروزرسانیهای سایت قرار دارد. اگر پیشنهاد یا انتقادی برای بهبود آموزش دارید، خوشحال میشیم به ما اطلاع بدهید.