نخستین دستور در پروسس یک انتساب متغیر است که مقداری به متغیر temp تخصیص می دهد. در مطالب آشنایی با مدل سازی رفتاری در VHDL بررسی کردیم که چگونه سیگنال ها مقادیری را پس از یک زمان مشخص یا یک تاخیر دلتا دریافت می کنند. انتساب متغیر بی درنگ در هنگام اجرای دستور اتفاق می افتد.

برای نمونه در مدل زیر، دستور نخست برای استفاده دستور دوم مقداری به متغیر temp تخصیص می دهد. انتساب متغیر فاقد تاخیر بوده و بی درنگ اتفاق می افتد.

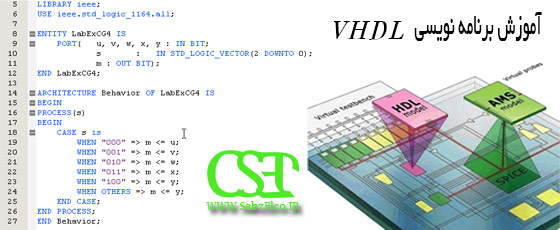

برای بیان شفاف تر این موضوع دو مثال را بررسی می کنیم. هر دو مثال مدل های یک مالتی پلکسر 4 به 1 می باشند. شکل بالا نماد و جدول درستی مالتی پلکسر را نشان می دهد. یکی از چهار سیگنال ورودی بسته به مقادیر ورودی های A و B به خروج منتشر می شود.

مدل اول مالتی پلکسر، یک مدل نادرست است و دومی تصحیح شده ی مدل اول است.

مثال Mux نادرست:

نقص مدل مالتی پلکسر باعث تولید نتایج نادرست می شود. این وضعیت در مدل زیر نشان داده شده است:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux IS

PORT (i0 , i1 , i2 , i3 , a , b , :IN std_logic;

Q : OUT std_logic);

END mux;

ARCHITECTURE wrong of mux IS

SIGNAL muxval : INTEGER;

BEGIN

PROCESS ( i0 , i1 , i2 , i3 , a , b )

BEGIN

Muxval <= 0;

IF (a = ‘1’) THEN

Muxval <= muxval + 1;

END IF;

IF (b = ‘1’) THEN

Muxval <= muxval +2;

END IF;

CASE muxval IS

WHEN 0 =>

Q <= I0 AFTER 10 ns;

WHEN 1 =>

Q <= I1 AFTER 10 ns;

WHEN 2 =>

Q <= I2 AFTER 10 ns;

WHEN 3 =>

Q <= I3 AFTER 10 ns;

WHEN OTHERS =>

NULL;

END CASE;

END PROCESS;

END wrong;

با تغییر مقدار یکی از سیگنال های ورودی در لیست حساسیت پروسس، دستورات ترتیبی پروسس اجرا می شوند.

دستور پروسس اولین مثال چهار دستور ترتیبی دارد. دستور اول سیگنال محلی muxval را با 0 مقداردهی اولیه می کند. دستوات بعدی بسته به مقدار سیگنال های ورودی a و b مقادیری را به سیگنال محلی اضافه می کنند. سرانجام دستور CASE برمبنای مقدار سیگنال muxval یک ورودی را برای انتشار به خروجی انتخاب می کند.

این مدل یک نقص مهم دارد. دستور (muxval <= 0) باعث می شود مقدار 0 به عنوان یک رویداد برای سیگنال muxval زمان بندی شود. در حقیقت، چون تاخیر مشخص نشده است مقدار 0 برای دلتای شبیه سازی بعدی زمان بندی می شود. هنگامی که دستور دوم،

IF (a = ‘1’) THEN

Muxval <= muxval + 1;

END IF;

اجرا می شود سیگنال muxval آخرین مقدار منتشر شده به آن را دارد. مقدار جدید زمان بندی شده از دستور اول هنوز منتشر نشده است. در حقیقت، هنگامی که یک دستور پروسس چندین تخصیص به یک سیگنال رخ می دهد، آخرین مقدار نخصیص یافته منتشر می شود.

سیگنال muxval هنگام ورود به پروسس مقدار ناخواسته دارد. تا پروسس اجرای تمام دستورات ترتیبی را تکمیل نکند این مقدار تغییر نمی کند. در واقع، اگر سیگنال b مقدار ‘1’ داشته باشد، به مقدار ناخواسته سیگنال در هنگام ورود به پروسس مقدار 2 اضافه می شود.

مثال بعدی روش بهتری برای پیاده سازی این مثال نشان می دهد. تنها تفاوت مدل بعدی با مدل قبلی در اعلان muxval و تخصیص به آن است. در مدل قبلی، muxval یک متغیر است و برای تخصیص مقدار به آن از تخصیص های متغیر استفاده می شود.

مثال Mux درست:

در این مثال، مدل نادرست برای انعکاس راه حل مشکلات مدل قبلی بازنویسی شده است:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux IS

PORT (i0 , i1 , i2 , i3 , a , b , :IN std_logic;

Q : OUT std_logic);

END mux;

ARCHITECTURE better of mux IS

SIGNAL muxval : INTEGER;

BEGIN

PROCESS ( i0 , i1 , i2 , i3 , a , b )

VARIABLE muxval : INTEGER;

BEGIN

Muxval := 0;

IF (a = ‘1’) THEN

Muxval := muxval + 1;

END IF;

IF (b = ‘1’) THEN

Muxval := muxval +2;

END IF;

CASE muxval IS

WHEN 0 =>

Q <= I0 AFTER 10 ns;

WHEN 1 =>

Q <= I1 AFTER 10 ns;

WHEN 2 =>

Q <= I2 AFTER 10 ns;

WHEN 3 =>

Q <= I3 AFTER 10 ns;

WHEN OTHERS =>

NULL;

END CASE;

END PROCESS;

END better;

این تفاوت جزئی در کد نویسی تفتوت عملیاتی چشمگیری ایجاد می کند.

با اجرای دستور (muxval :=0)، مقدار صفر بی درنگ در متغیر muxval قرار می گیرد. مقدار زمان بندی نمی شود زیرا در این مثال، muxval متغیر است نه سیگنال، متغیرها برخلاف سیگنال ها که نشان دهنده اتصالات داخلی مدار می باشند، حافظه های محلی را نشان می دهند. حافظه های محلی بی درنگ به روز می شوند و مقدار جدید را می توان برای محاسبات بعدی در مدل استفاده کرد.

چون بی درنگ به muxval مقدار اولیه داده می شود، دو دستور بعدی در پروسس صفر را به عنوان مقار اولیه استفاده می کنند و بسته به مقدار سیگنال های a و b اعداد مناسب را اضافه می کنند. این تخصیص ها نیز بی درنگ می باشند، بنابراین هنگام اجرای دستور CASE، متغیر muxval مقدار صحیحی دارد. از این مقدار، سیگنال ورودی درست به خروجی منتشر می شود.

این آموزش بیش از ۳ سال قبل ارسال شده و اکنون در لیست بهروزرسانیهای سایت قرار دارد. اگر پیشنهاد یا انتقادی برای بهبود آموزش دارید، خوشحال میشیم به ما اطلاع بدهید.

ممنون