پروسس هایی که در بخش دستوری یک موجودیت وجود دارند پروسس های غیرفعال نامیده می شوند.

پروسس های غیرفعال با پروسس های نرمال تفاوت داشته و انتساب سیگنال در آنها مجاز نیست. این پروسس ها در تمام توابع بررسی استفاده می شوند.

برای نمونه، یک استنفاده مناسب از پروسس غیرفعال، بررسی زمان نشست داده روی فلیپ فلاپ است.

مزیت پروسس غیرفعال نسبت به مثال تشریح شده در بخش دستور ASSERT این است که چون پروسس غیرفعال در موجودیت وجود دارد، برای تمام معماری موجودیت قابل استفاده است.

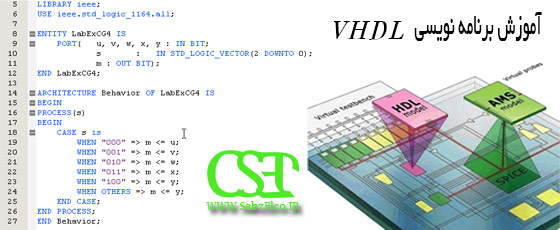

حال مثال زیر را بررسی می کنیم:

LIBRARY IEEE;

USE IEEE.std_logic_1164ALL;

ENTITY dff IS

PORT ( CLK , din : IN std_logic;

Q , QB : OUT std_logic);

BEGIN

PROCESS(CLK , din)

VARIABLE last_d_change : TIME := 0 ns;

VARIABLE last_clk, last_d_value : std_logic := ‘x’;

BEGIN

IF ( din /= last_d_value ) THEN

Last_d_change := now;

Last_d_value := din;

END IF;

IF ( CLK /= last_clk ) THEN

IF ( CLK = ‘1’ ) THEN

ASSERT ( now – last_d_change >= 15 ns )

REPORT “setup error”

SEVERITY ERROR;

END IF;

Last_clk := CLK ;

END IF;

END PROCESS;

END dff;

ARCHITECTURE behave OF dff IS

BEGIN

.

.

.

.

END behave;

ARCHITECTURE struct OF dff IS

BEGIN

.

.

.

.

END struct;

ARCHITECTURE switch OF dff IS

BEGIN

.

.

.

.

END switch;

این مثال موجودیت یک فلیپ فلاپ D با پروسس غیرفعال اضافه شده به آن را نشان می دهد که نشست داده را نسبت به ساعت بررسی می کند.

این تابع بررسی زمان نشست هنگام توصیف دستور ASSERT با جزئیات کامل را تشریح کرد.

این مثال نشان می دهد که با اضافه کردن تابع بررسی زمان نشست در بخش دستوری موجودیت، بطور خودکار در تمام معماری های موجودیت بررسی نشست داده انجام می شود.

بدون این عملکرد، هر یک از معماری ها مجبور خواهند بود که بررسی نشست را داشته باشند. این کار حجم کد را افزایش داده و می تواند بین معماری ها ناسازکاری بوجود آورد.

همان طور که اشاره کردیم تنها قیدی که روی پروسس های غیرفعال وجود دارد مجاز نبودن انتساب سیگنال است.

در مثال بالا برای نشان دادن یک پروسس غیرفعال از یک دستور پروسس استفاده شد.

پروسس غیرفعال را به صورت یک دستور همزمان نیز می توان استفاده کرد که هیچ انتساب سیگنالی انجام نمی دهد. دستور ASSERT همزمان و فراخوانی های زیربرنامه همزمان، مثال هایی از این دست می باشند.

در مثال زیر دو دستور ASSERT به عنوان پروسس های غیرفعال نشان داده شده اند:

ENTITY adder IS

PORT ( A , B : IN INTEGER;

X : OUT INTEGER);

BEGIN

ASSERT ( A < 256 )

REPORT “A out of range”

SEVERITY ERROR;

ASSERT ( B < 256 )

REPORT “B out of range”

SEVERITY ERROR;

END adder;

نخستین دستور ASSERT خارج از بازه نبودن ورودی A را جهت اطمینان بررسی می کند، و دستور دوم ورودی B را بررسی می کند تا خارج از بازه جمع کننده نباشد.

هر یک از این دستورها به صورت پروسسی مجزا عمل می کند که به سیگنال درون عبارتش حساس است. برای نمونه، نخستین دستور تاکیدی به سیگنال A حساس است زیرا سیگنال A در عبارت آن وجود دارد.

این آموزش بیش از ۳ سال قبل ارسال شده و اکنون در لیست بهروزرسانیهای سایت قرار دارد. اگر پیشنهاد یا انتقادی برای بهبود آموزش دارید، خوشحال میشیم به ما اطلاع بدهید.